منطق ترانزستور ترانزستور

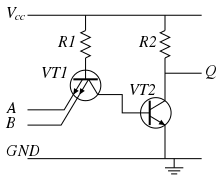

منطق ترانزستور ترانزستور (بالإنجليزية: TTL- Transistor Transistor Logic) هو أحد عوائل الدارات الرقمية المبنية من ترانزستورات ثنائية القطبية (BJT)، ومقاومات. تعرف باسم منطق ترانزستور-ترانزستور لأن وظيفتي البوابة المنطقية (AND، على سبيل المثال) والتضخيم تتم بواسطة ترانزستور (مقارنة بـ RTL وDTL).

استخدمت الدارات المتكاملة TTL على نطاق واسع في التطبيقات التقنية مثل (أجهزة الكمبيوتر وأجهزة التحكم الصناعية ومعدات الاختبار والقياس) يتم استخدام TTL أحيانا للأشارة إلى TTL-compatible logic levels [الإنجليزية]، فعلى سبيل المثال تستخدم كتسمية لمدخلات ومخرجات الأدوات الإلكترونية.[1]

العائلات الفرعية[عدل]

يتضمن منطق ترانزستور ترانزستور عدة عائلات فرعية هي:

- العائلة القياسية (بالإنجليزية: Standered TTL)

- العائلة المنخفضة القدرة (بالإنجليزية: Low power TTL)

تتميز عن العائلة القياسية بأن التيار المار فيها أقل وضياع القدرة فيها أقل.

- العائلة عالية السرعة (بالإنجليزية: High speed TTL)

وتتميز بسرعة الانتقال بين الحالات المنطقية بسبب استخدام زوج دارلينغتون فيها.

- عائلة (بالإنجليزية: Shottky clamped TTL)

- عائلة الشوتكى مخفضة القدرة (بالإنجليزية: Low power Shottky)

وهي آخر العائلات الفرعية ظهورا وتعتبر أسرع من أي عائلة TTL أخرى وتختلف هذه العائلة الفرعية عن أي عائلة أخرى في الTTL في أنها تستخدم ترانزستور معدل حيث توصل قاعدة الترانزستور بمجمعه عن طريق موحد شوتكي ويعمل الدايود على تحويل تيار القاعدة عندما يكون الترانزستور في حالة غلق الدائرة ON، وذلك حتى يمنعه من تخزين الشحنات التي تبطئ من سرعته عندما يتحول من الحالة ON إلى حالة فتح الدائرة OFF. وهذا يسرع الأداء العام للدارة.

عمود «توتيم»[عدل]

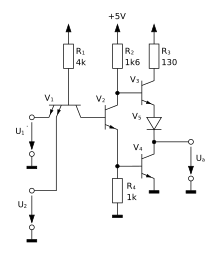

«توتيم بول» أو «عمود توتيم» يعني إضافة ترانزستورين ثنائيا القطبية، مقاومة وصمام ثنائي عند مخرج الدائرة.

ان إضافة دائرة توتيم بول عند المخرج تساعد على تخطي بعض المشاكل المتعلقة بالسرعة، والتي تواجهها دائرة منطق ترانزستور ترانزستور العادية.

-

دائرة ترانزيستور ترانزيستور القياسية باستخدام "عمود توتيم"

الجدول ادناه يوضح أهمية كل عنصر في دائرة منطق ترانزستور ترانزستور.

| لعنصر | الوظيفة |

| T1 | ترانزيستور ثنائي القطبية متعدد البواعث |

| T2 | توفير تيار لقيادة ت4 |

| T3 | يقوم برفع تيار المصدر للاعلى |

| T4 | ترانزيستور يقوم بوظيفة "ليس" |

| R1 | مقاومة للحد من تيار القاعدة |

| R2 | تقوم (بالتوافق مع ت2) باجراء منطق "ليس" |

| R4 | جزء من عملية سحب التيار للاعلى |

| يساعد على تفريغ ت4 | |

| D1 | للحد من تأرجح المدخلات (غير موجود بالصورة) |

خصائص دالة تحويل الجهد [عدل]

الرسوم البيانية غير متاحةٍ مؤقتًا لأسبابٍ تقنيَّة. |

يلاحظ وجود 3 حالات للمخرج (مرتفع، ج، ومنخفض)، والذي يختلف باختلاف الجهد المدخل للدارة، حيث أنه من الممكن تقسيم الجهد المدخل لثلاث فئات أيضا (مرتفع، منخفض، وج).

الجدول ادناه يوضح حالة كل عنصر في حالات المخرجات الثلاث.

| العنصر | مخرج مرتفع | مخرج ج | مخرج منخفض |

| T1 | مشبع | مشبع | نشط عكسي |

| T2 | متوقف | نشط | مشبع |

| T3 | على حافة النشط | نشط | متوقف |

| D1 | على حافة النشط | على حافة النشط | متوقف |

| T4 | متوقف | على حافة الايصال | مشبع |

اقرأ أيضا[عدل]

المراجع[عدل]

- ^ Eren، H. (2003)، Electronic Portable Instruments: Design and Applications، CRC Press، ISBN:0-8493-1998-6، مؤرشف من الأصل في 2015-05-11

| في كومنز صور وملفات عن: منطق ترانزستور ترانزستور |